Giriş

Tarihsel olarak FPGA’lar için (Alanda Programlanabilir Kapı Dizileri, (-ing. Field Programmable Gate Array) birincil optimizasyon metrikleri çalışma frekansı (Fmax)ve kaynak kullanımı (Alan) iken, modern sistem tasarımında güç tüketimi baskın kısıtlama olarak ortaya çıkmıştır. Bu değişim, yüksek performanslı bilgi işlemede termal sınırların doygunluğa ulaşması ve pille çalışan uç (-ing. edge) cihazların yaygınlaşması ile doğrudan ilişkilidir. Yapılan bir çalışmaya göre [1], FPGA’ların uygulamaya ve esnekliğine bağlı olarak ASIC’lere göre 3-4 kat daha yavaş, 5-35 kat daha büyük ve 7-14 kat daha az enerji verimli olduğu tahmin edilmektedir.

Bu yazıda FPGA’lar için düşük güç tasarım tekniklerinin RTL (Yazmaç Aktarım Seviyesi, -ing. Register Transfer Level) ile ilgili olan kısmı incelenmiştir. Okuyucunun doğrudan uygulayabileceği tekniklere yer verilmiştir. Anlatım teoride kalmayıp kodlar <ve sentez sonuçları> üzerinden somut olarak gösterilmiştir. Yongaların sistem seviyesinde mimari tasarım kararları ile yapılan güç optimizasyonları, başka bir blog yazısının konusu olacaktır.

1. Temel Bilgiler

Güç tüketimini azaltmak için kullanılan stratejilere geçmeden önce güç kaybının altında yatan mekanizmaların ayrıştırılması gerekmektedir. FPGA’lardaki toplam güç tüketimi (Ptotal), statik güç (Pstatic) ve dinamik gücün (Pdynamic) toplamıdır; buna ek olarak, genellikle I/O gücü olarak kategorize edilen ve dış dünya ile etkileşimi yöneten önemli bir bileşen de mevcuttur.

1.1 Statik Güç

Statik güç, diğer bir adıyla sızıntı (-ing. leakage) gücü, cihazın gücü açık olduğu ancak saat sinyalinin (clock) tetiklenmediği durumlarda tükettiği enerjiyi temsil eder. Yani devre anahtarlama yapmasa bile transistörlerin içindeki sızıntı akımından kaynaklanır. Statik güç kaybı, fiziksel yapıya bağlıdır. Ancak yine de bazı tekniklerle RTL kodlama seviyesinde HDL (Donanım Tanımlama Dilleri, -ing. Hardware Description Languages) dilleri ile güç kaybı minimize edilebilir. İleri ki başlıklarda bu konu ele alınacak ve kod örneği gösterilecektir.

Statik gücü yöneten temel denklem şu şekildedir:

Burada , sıcaklığa ve üretim mimarisine büyük ölçüde bağımlıdır. Sıcaklık ile sızıntı akımı arasındaki ilişki üsteldir; dinamik anahtarlama nedeniyle cihaz ısındıkça, sızıntı akımı artar, bu da sıcaklığı daha da yükselterek harcanan gücü arttırır [2].

1.2 Dinamik (Anahtarlama) Güç

Dinamik güç, bir FPGA’daki sinyallerin her anahtarlama (-ing. switching) yaptığında (0’dan 1’e veya 1’den 0’a geçme durumu) oluşan güç tüketimidir. FPGA tasarımcısının doğrudan kontrolü altında olan en büyük güç bileşenidir.

Dinamik gücü yöneten temel fiziksel denklem şöyledir:

Bu formüldeki değişkenler şunlardır:

- (Aktivite Faktörü): Bir sinyalin ne kadar sık 0↔1 değiştiğini gösterir. Sinyal ne kadar çok değişirse, güç o kadar artar.

- (Yük Kapasitansı): Anahtarlanan toplam kapasitans (kapı ve tel kapasitansları toplamı). Devre büyüklüğüne göre artar.

- (Besleme Voltajı): Çekirdek çalışma voltajı, FPGA’nın çalıştığı voltajdır.

- (Frekans): Saat sinyalinin (clock) frekansı.

Voltaj () ile güç arasındaki karesel ilişki, voltaj ölçeklemenin teorik olarak en önemli güç azaltma yöntemi olduğunu göstermektedir. Voltajın düşürülmesi, güç tüketimini karesel olarak azaltırken, transistörlerin anahtarlama hızını düşürerek zamanlama kapanışını (-ing. timing closure) zorlaştırır. Bu durum, güç ve performans arasında hassas bir denge kurulmasını gerektirir.

Dinamik güce ek olarak, Kısa Devre Gücü (-ing. Short-Circuit Power) bileşeni de vardır. Bu, bir CMOS kapısında sinyal değişirken PMOS ve NMOS transistörlerinin çok kısa bir an için aynı anda iletime geçmesinden kaynaklanır. Bu anda besleme ile toprak arasında geçici bir akım yolu oluşur. Eğer sinyal çok yavaş yükselip düşüyorsa (-ing. slew rate), bu iki transistörün aynı anda iletimde kaldığı süre uzar ve bu da ekstra güç tüketimine yol açar.

1.3 FPGA Güç Tüketimi Dağılımı

Anahtarlama davranışının yüksek kapasitansı nedeniyle, ara bağlantı ağı (routing) genellikle dinamik gücün en büyük kısmını oluşturur. Aşağıdaki tabloda Tipik FPGA tasarımlarında güç dağılımı ve optimizasyon potansiyellerine yer verilmiştir.

| Bileşen | Yaklaşık Güç Katkısı | Baskın Güç Türü | Optimizasyon Potansiyeli |

|---|---|---|---|

| Saat Ağı (Clock Network) | %30 – %40 | Dinamik | Yüksek (Clock Gating ile) |

| Mantık (LUTs/FFs) | %20 – %30 | Dinamik & Statik | Orta (RTL Kodlama ile) |

| Ara Bağlantı (Interconnect) | %30 – %50 | Dinamik | Orta (Yerleştirme ile) |

| I/O Arayüzleri | Değişken (>%50 olabilir) | I/O (Yük Bağımlı) | Yüksek (Standart Seçimi ile) |

| Blok RAM (BRAM) | %10 – %20 | Statik (Sızıntı) | Yüksek (Enable Sinyalleri ile) |

2. RTL Optimizasyon Teknikleri

Cihaz seçimi taban çizgiyi belirlerken, RTL tasarımı dinamik güç profilini şekillendirir. Bu aşamadaki temel amaç, anahtarlama aktivitesini () en aza indirmek ve yük kapasitansını () azaltmaktır.

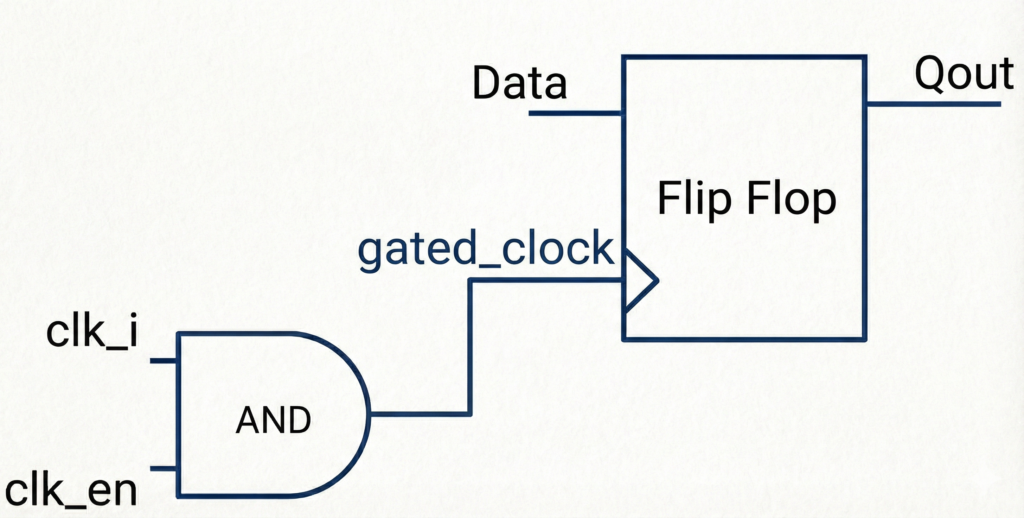

2.1 Saat Kapılama (Clock Gating)

Saat kapılama, dinamik gücü azaltmak için en etkili RTL tekniğidir. Verisi değişmeyen bir yazmacın (-ing. register) saat sinyalinin devre dışı bırakılmasıyla, hem saat ağacındaki hem de yazmacın kendisindeki anahtarlama aktivitesi ortadan kaldırılır.

Saat kapılama tekniğini elle yapmak önerilmez. Modern sentez araçları (Vivado, Quartus vb.), HDL kodunda senkron bir “enable” (etkinleştirme) koşulu tespit ettiğinde otomatik olarak saat kapılama uygular. Aşağıda basit bir Verilog örneğine yer verilmiştir.

// Sentez aracı bunu clock enable (CE) pinine veya BUFGCE'ye dönüştürür

always @(posedge clk) begin

if (enable) begin

q <= d;

end

// else durumu yok, yani enable düşükse q eski değerini korur

endBu senaryoda, sentez aracı flip-flop üzerindeki CE pinini kullanır veya fan-out (sürüm kapasitesi) yeterince büyükse bir BUFGCE (Clock Enable özellikli Global Saat Tamponu) ekler.

Tasarım Uyarısı: Tasarımcılar, mantık kapıları kullanarak manuel saat kapılama yapmaktan (örneğin assign gclk = clk & enable) kaçınmalıdır. Bu yöntem, FPGA kumaşında “gated clock” yapıları oluşturur ve bu yapılar “glitch” (istenmeyen sinyal sıçramaları) ve “skew” (zamanlama kayması) sorunlarına yol açarak zamanlama kapanışını imkansız hale getirebilir. Bunun yerine, FPGA’nın saat kaynakları (BUFGCE, BUFHCE) kullanılmalıdır [3].

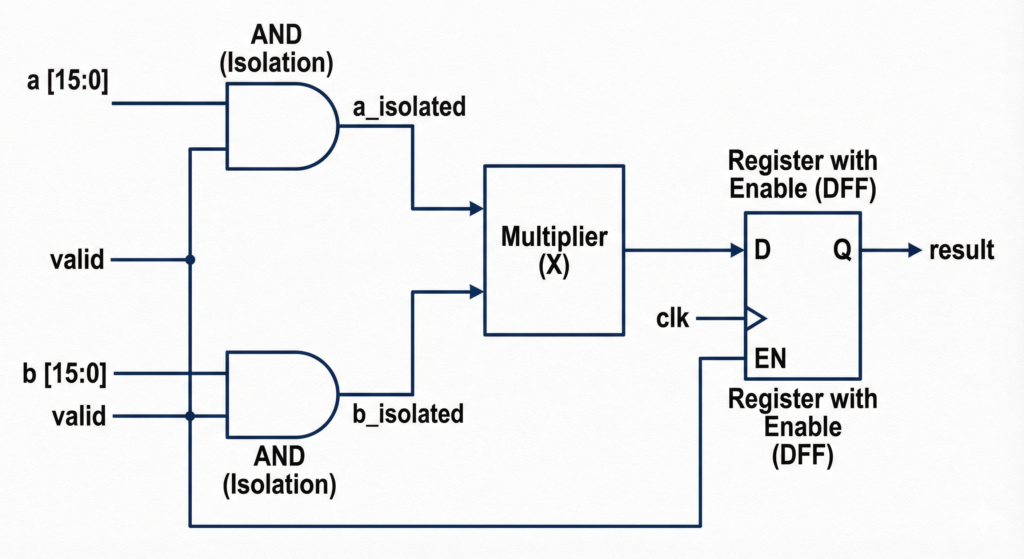

2.2 İşlenen İzolasyonu (Operand Isolation)

İşlenen izolasyonu, bir kombinasyonel mantık bloğunun sonucu kullanılmayacaksa, girişlerindeki anahtarlama aktivitesinin bu bloğa yayılmasını önlemek için kullanılan bir tekniktir. Yani kullanılmayan kullanılmayan modülün girişleri sabitlenir, böylece anahtarlama aktivitesi azalır.

Örnek senaryo ve çözüm:

Sonucu sadece valid sinyali yüksek olduğunda örneklenen bir DSP çarpıcısı düşünelim. Eğer valid sinyali düşükken çarpıcının girişleri değişmeye devam ederse, çarpıcı gereksiz yere dinamik güç tüketecektir. Girişleri valid sinyali ile VE (AND) işlemine tabi tutarak, birim boşta iken girişlerin sıfıra zorlanması sağlanır. Aşağıda senaryo koduna yer verilmiştir:

// İzolasyon Öncesi (Verimsiz)

always @(posedge clk) begin

if (valid) result <= a * b; // Çarpıcı girişleri her zaman aktiftir

end

// Manuel İzolasyon Sonrası (Verimli)

wire [15:0] a_isolated = valid? a : 16'b0;

wire [15:0] b_isolated = valid? b : 16'b0;

always @(posedge clk) begin

if (valid) result <= a_isolated * b_isolated;

endVivado gibi araçlar set_power_opt -operand_isolation komutu ile bunu otomatik yapabilse de [4], DSP blokları gibi yüksek kapasitanslı yollarda manuel uygulama deterministik sonuçlar verir. Bu teknik, özellikle geniş veri yolları ve aritmetik operatörler için %5-15 arasında dinamik güç tasarrufu sağlayabilir [4],[5].

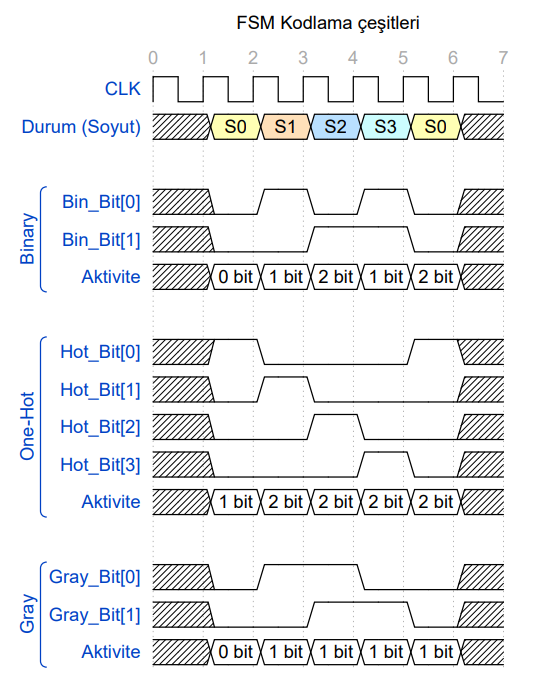

2.3 Sonlu Durum Makinesi (FSM) Kodlaması

FSM (Sonlu Durum Makinesi, -ing. Finite State Machine) durum kodlamasının seçimi, durum yazmacının anahtarlama aktivitesini ve bir sonraki durum kod çözme mantığının karmaşıklığını etkiler. FSM durum kodlamaları:

İkili (Binary) Kodlama: En az sayıda bit kullanır (). Ancak, durum geçişleri sırasında birden fazla bitin aynı anda değişmesi (örneğin 011’den 100’e geçişte 3 bit değişir) yüksek anahtarlama aktivitesine neden olur.

One-Hot Kodlama: Her durum için bir bit kullanır ( bit). Geçişler her zaman tam olarak iki bitlik değişim içerir (biri düşer, diğeri yükselir). Flip-flop sayısı artar ancak FPGA’lar flip-flop açısından zengindir. One-hot, bir sonraki durum mantığını basitleştirir (genellikle basit karşılaştırıcılara indirger), bu da kombinasyonel buluttaki glitch gücünü azaltır.

Gray Kodlama: Her geçişte sadece bir bit değişir. Sıralı ilerleyen sayaçlar veya FSM’ler için optimaldir ve anahtarlama aktivitesini en aza indirir.

Aşağıdaki görselde 4 durumlu bir sonlu durum makinesi (FSM) için ikili, one hot, gray kodlama davranışları dalga formu olarak gösterilmiştir.

Yüksek hızlı ve karmaşık FSM’ler için One-Hot performans ve güç dengesi açısından genellikle tercih edilirken, yavaş ve sıralı sayaçlar için Gray kodlama üstündür. Aşağıda bu üç teknik için karşılaştırma tablosuna yer verilmiştir.

| Özellik | Binary (İkili) | One-Hot | Gray Code |

| Bit Sayısı (Flip-Flop) | En Az () (Alan tasarrufu) | En Çok () (Alan masraflı) | En Az () (Alan tasarrufu) |

| Mantık Karmaşıklığı (LUT) | Yüksek (Durum çözmek zordur) | Düşük (Kıyaslama basittir) | Orta (Sıralı değilse zorlaşır) |

| Çalışma Hızı () | Düşük | En Yüksek (Kombinasyonel yol kısadır) | Orta |

| Güç Tüketimi | Yüksek (Çok bit değişir, Glitch boldur) | Orta / Kararlı (Sabit 2-bit değişir) | En Düşük (Sadece 1-bit değişir) |

| Glitch Riski | Çok Yüksek (Ara geçişler oluşur) | Düşük (Yol dengelidir) | Yok (Yarış durumu oluşmaz) |

| En İyi Kullanım Senaryosu | Alanın (FF) çok kısıtlı olduğu basit tasarımlar. | Yüksek Hız ve karmaşık durum geçişleri gerektiren tasarımlar. | Low Power (Pil Ömrü) ve sıralı sayaç/kontrolcü tasarımları. |

2.4 Çapak (-ing. Glitch) Azaltma

Kısa zamanlı “kararsızlık” anları, büyük aritmetik devrelerde devasa bir güç israfına dönüşür. Bir FPGA devresinde Dinamik Güç, sinyal 0->1 veya 1->0 olduğunda harcanır. İdeal dünyada bir sinyal değişmesi gerektiğinde sadece 1 kez değişir. Gerçek dünyada ise, özellikle kombinasyonel devrelerde giriş sinyalleri farklı yollardan (farklı gecikmelerle) geldiği için çıkış sinyali, son haline oturana kadar birkaç kez dalgalanır. İşte bu işe yaramayan ara geçişlere Glitch denir.

İstenmeyen Glitch 3 yöntemle minimize edilebilir: yol dengeleme(-ing. path balancing), boru hattı ekleme (-ing. pipelining) ve daha önceden de gördüğümüz işlenen izolasyonu (-ing. operand isolation)

1. Yol Dengeleme:

Glitch’in ana sebebi Skew (varış zamanı farkı). Eğer sinyallerin varış sürelerini eşitlersek, glitch oluşamaz. Örneğin: sonuc = A + B + C + D yapmak yerine sonuc = ((A + B) + (C + D)) yapmak daha sağlıklıdır. Böylelikle A+B gerçekleşirken C+D paralel olarak gerçekleşir ve aynı anda çıkan sonuçlar toplanarak sonuç elde edilir. Sentez araçları bu basit örnek için optimizasyon gerçekleştirebilir. Ancak daha kompleks tasarımlarda signed unsigned toplamları veya farklı bit genişliklerinde optimizasyonu gerçekleştirmez. Bu yüzden en sağlıklısı optimizasyonu manuel olarak yapmaktır.

2. Boru Hattı Ekleme (Pipelining):

Glitchlerin yayılmasını fiziksel olarak durduran en etkili yöntemdir. Uzun kombinasyonel mantık bloklarının (Combinational Cloud) arasına Register (Flip-Flop) konulur. Glitchler kombinasyonel mantıkta oluşur ama Registerlardan geçemez. Register, sadece saat darbesi (clock edge) geldiğinde veriyi örnekler. O sırada glitch çoktan sönmüş ve sinyal oturmuş olur. Register koymak “latency”yi (gecikme süresini) artırır ama glitchlerin bir sonraki bloğa geçip orada güç harcamasını tamamen engeller [7].

2.5 Bellek-Hafıza Optimizasyonu

Bellek mimarisi seçimi gücü önemli ölçüde etkiler. Dağıtık RAM (LUTRAM), FPGA mantık kumaşından oluşturulur. Esnektir ancak büyük bloklar için kullanıldığında, LUT’ları birbirine bağlamak için gereken yoğun yönlendirme (routing) nedeniyle güç açısından verimsizdir. Blok RAM’ler (BRAM’ler) ise sert makrolardır ve bit başına güç verimliliği çok daha yüksektir. Modern BRAM’ler (UltraScale ve Agilex gibi) ardışık (cascadable) modlara ve uyku (sleep) modlarına sahiptir [3],[5]. BRAM’ler saat sinyali aktifken güç tüketir.

1. BRAM Kullanımı

BRAM kullanırken yapılabilecek kritik hatalardan biri de yazma durumu için sadece Write_Enable pinini kullanmaktır. WE = 0 iken hafıza yazmaz ama EN = 1 bırakılırsa içerideki saat dağıtım ağı (clock network) ve okuma yükselteçleri (sense amplifiers) hala çalışır ve güç tüketir. Eğer o cycle’da okuma ya da yazma yapılmıyorsa, EN pini 0 yapılmalı. Bir BRAM bloğu EN pini 0 iken (Disable durumu), EN pini 1 olduğu duruma göre dinamik güçte %99’a varan tasarruf sağlar [3]. Sadece çok küçük bir statik (leakage) güç harcar [Kaynak: Xilinx UltraFast Design Methodology Guide (UG949): “Use the Block RAM Enable Pin… Disabling the enable pin effectively gates the clock to the memory, eliminating dynamic power consumption.”]

2. Derin Hafızalar İçin Kaskat Yapı

Eğer mevcut projede çok derin hafız kullanımı (64K gibi) söz konusuysa derleyici birden fazla BRAM bloğu kullanarak sentezler. İki çeşit yaklaşım vardır: İlki tüm BRAM blokları aktiftir ve çıkışları tek büyük bir mux’a bağlıdır. Mux, BRAM’ler arasından hangisinin okunacağını seçer. Bu yaklaşım güç tüketimini arttırır. Çünkü kullanılmayan BRAM blokları da aktiftir. İkinci yaklaşım ise kaskat yapı kurmaktır. Sadece ilgili olan BRAM bloğu aktif edilir ve veri çekilir. Daha iyi anlaşılması için şöyle basit bir kütüphaneci analoji kurabiliriz:

Varsayalım ki elimizde 2000 sayfalık dev bir ansiklopedi var. Ama bizim masamızda (FPGA içinde) sadece 1000 sayfalık kitapları koyabileceğimiz 2 tane raf (RAM Blokları) var. Ansiklopediyi ikiye böleriz;

Cilt 1: 0 – 999. sayfalar (RAM_A)

Cilt 2: 1000 – 1999. sayfalar (RAM_B)

Paralel Bağlantı (Kötü – Yüksek Güç): 500. sayfayı okumak istiyoruz. Kütüphaneci gidip hem Cilt 1’i hem de Cilt 2’yi aynı anda açıyor, ışıklarını yakıyor. Sonra sana “Hangisi lazımdı?” diye soruyor. Sen Cilt 1’i alıyorsun, Cilt 2 boş yere açık bekliyor. 2 birim güç harcandı (Biri boşa gitti).

Kaskat Bağlantı (İyi – Low Power): 500. sayfayı istedik. Kütüphaneci bakıyor: “500 sayısı 1000’den küçük, demek ki bu Cilt 1’de.” Gidip sadece Cilt 1’in ışığını yakıyor. Cilt 2 karanlıkta ve kapalı kalıyor. 1 birim güç harcandı (%50 tasaaruf).

Aşağıda kaskat bağlantı için örnek bir verilog kodu verilmiştir.

// 2048 Derinlikli Hafıza (İki tane 1024'lük bloktan oluşur)

// Adres 11 bit: [10] -> MSB (Seçici Bit), [9:0] -> Blok içi adres

wire [10:0] full_address;

wire bank_select = full_address[10]; // En anlamlı bit (0 ise Bank0, 1 ise Bank1)

// --- RAM 0 ---

// Sadece bank_select 0 ise çalışır!

my_bram RAM_0 (

.clk(clk),

.addr(full_address[9:0]),

.en (sys_en && (bank_select == 1'b0)), // Kaskat Mantığı

.dout(data_0)

);

// --- RAM 1 ---

// Sadece bank_select 1 ise çalışır!

my_bram RAM_1 (

.clk(clk),

.addr(full_address[9:0]),

.en (sys_en && (bank_select == 1'b1)), // Kaskat Mantığı

.dout(data_1)

);

// Çıkış MUX'u

assign data_out = (bank_select == 1'b0) ? data_0 : data_1;3. Distributed RAM vs. Block RAM Seçimi

Tasarımında küçük hafızalar (FIFO’lar veya küçük Look-up Table’lar gibi) kullanılıyorsa yanlış türü seçmek güç tüketimini artırır. Yapılacak olan seçimi FPGA’nın fiziksel özellikleri belirler. Mesela modern Xilinx FPGA’lerinde (7-Series, UltraScale, Versal) temel yapı taşı olan LUT (Look-Up Table), 6 girişlidir (LUT6). Donanımsal olarak 64-bit derinliğinde ve 1-bit genişliğinde (64×1) bir RAM olarak yapılandırılabilir demektir. Eğer 64 bit kadar küçük bir veri saklanacaksa bu iş için BRAM kullanmak, bir bardak su içmek için barajın kapağını açmaya benzer. Hem statik güç (sızıntı) israfıdır hem de BRAM kaynağını tüketir.

Hafızada saklanmak istenen veri boyutu arttıkça LUT kullanmak Kullanılan LUT’ların sayısı arttıkça onları bağlayan kablo sayısı, LUT’ları da ciddi miktarda artmaya başlarkablo gerekir. Glitch riski tavan yapar. Dinamik güç çok artar.

2.6 Veri Yolu Tersine Çevirme Kodlaması (-ing. Data Bus Inversion – DBI)

Geniş veri yolları (harici bellek arayüzleri gibi) için Veri Yolu Tersine Çevirme güçlü bir tekniktir. Bir bayt içindeki bitlerin %50’sinden fazlası bir önceki duruma göre değişiyorsa (Hamming mesafesi > N/2), verici veriyi tersine çevirir (invert eder) ve bir “DBI” bayrak biti set eder. Örneğin, 00000000‘dan 11111111‘e geçmek yerine, veri ters çevrilerek 00000000 olarak gönderilir ve DBI biti 1 yapılır. Böylece veri yolu üzerindeki geçiş yapan bit sayısı hiçbir zaman veri yolu genişliğinin %50’sini geçmez. Bu, I/O bankasının maksimum dinamik güç tüketimini sınırlar ve Eşzamanlı Anahtarlama Gürültüsünü (-ing. Simultaneous Switching Noise – SSN) azaltır. LPDDR4 arayüzlerinde standart olan bu teknik [8], özel veri yollarında manuel olarak da uygulanabilir.

Sonuç

FPGA tasarımında güç optimizasyonu, artık performans ve alan kadar kritik bir tasarım metriği haline gelmiştir. Bu yazıda incelediğimiz RTL seviyesindeki teknikler, tasarımcılara doğrudan uygulayabilecekleri somut çözümler sunmaktadır.

Ele aldığımız yöntemleri ve etkilerini özetleyecek olursak:

Yüksek Etki – Düşük Maliyet:

- Saat kapılama (Clock Gating): %30-40’lık güç tasarrufu potansiyeli

- BRAM enable sinyali yönetimi: Kullanılmayan bloklarda %99’a varan dinamik güç tasarrufu

- İşlenen izolasyonu: DSP blokları ve geniş veri yollarında %5-15 tasarruf

Orta Etki – Dikkatli Uygulama Gerektirir:

- FSM kodlama stratejisi: Durum makinesi karmaşıklığına bağlı olarak değişken tasarruf

- Glitch azaltma: Kombinasyonel bulut yoğunluğuna göre %10-20 potansiyel

- Kaskat bellek yapıları: Derin hafızalarda %50’ye varan kullanım dışı blok gücü tasarrufu

Özel Senaryolar:

- DBI kodlaması: Geniş I/O arayüzlerinde SSN azaltımı ve güç dengeleme

Kritik nokta şudur: Bu tekniklerin çoğu birbirleriyle sinerjik çalışır. Örneğin, saat kapılama ile işlenen izolasyonunu birleştirmek, tek başına uygulamalarından daha yüksek kazanç sağlar. Benzer şekilde, boru hattı ekleme hem glitch’leri azaltır hem de saat kapılama için daha iyi fırsatlar yaratır. Modern sentez araçları (Vivado, Quartus) bu optimizasyonların bazılarını otomatik uygulasa da, tasarımcının bilinçli RTL kodlaması hala belirleyicidir. Özellikle yüksek fan-out’lu sinyaller, DSP blokları ve bellek arayüzleri gibi kritik noktalarda manuel müdahale, araç sezgilerinden daha deterministik sonuçlar verir.

Gelecek yazımızda, bu RTL tekniklerini tamamlayacak sistem seviyesi kararları ele alacağız: voltaj/frekans ölçekleme (DVFS), güç alanları (power domains), kısmi yeniden yapılandırma (partial reconfiguration) ve uyarlamalı saat ağacı tasarımı gibi konular, çip seviyesinde güç optimizasyonunun daha üst katmanlarını oluşturacak.

İleri Okumalar

Temel Kaynaklar

FPGA Üreticilerinin Güç Analizi Kılavuzları

- Xilinx, “Vivado Design Suite User Guide: Power Analysis and Optimization (UG907)” — Vivado’nun güç analizi araçlarının kapsamlı kullanımı, power constraint’ler ve raporlama

- Intel, “Power Analysis and Optimization User Guide (Quartus Prime)” — Intel FPGA’lar için güç tahminleme ve optimizasyon akışı

- Xilinx, “7 Series FPGAs Power Management (UG483)” — Uyku modları, güç sekanslaması ve termal yönetim

Akademik Temeller

- J. M. Rabaey, A. Chandrakasan, and B. Nikolić, “Digital Integrated Circuits: A Design Perspective” — CMOS güç tüketiminin fiziksel temelleri için altın standart

- K. K. Parhi, “VLSI Digital Signal Processing Systems” — Pipelining, retiming ve düşük güç DSP mimarileri

Konulara Göre Detaylı Okumalar için

Saat Ağı ve Saat Kapılama

- Xilinx, “UltraScale Architecture Clocking Resources (UG572)” — BUFGCE, BUFHCE ve saat ağı mimarisi detayları

- P. Djekic et al., “Clock Gating Techniques for Low Power Design” — Otomatik ve manuel clock gating stratejileri karşılaştırması

Bellek Optimizasyonu

- Xilinx, “UltraScale Memory Resources (UG573)” — BRAM, URAM ve dağıtık RAM kullanım senaryoları

- M. Horowitz, “Computing’s Energy Problem” (Stanford) — Bellek erişiminin enerji maliyeti üzerine perspektif

FSM ve Kodlama Teknikleri

- S. Palnitkar, “Verilog HDL: A Guide to Digital Design and Synthesis” — FSM kodlama stilleri ve sentez sonuçları

- C. E. Cummings, “Synthesizable Finite State Machine Design Techniques” (SNUG Paper) — Endüstri standardı FSM yazım pratikleri

Gelişmiş Güç Yönetimi

- Xilinx, “Zynq UltraScale+ MPSoC Power Management (UG1085)” — Power domains, DVFS ve sistem seviyesi güç yönetimi

- Intel, “Stratix 10 Power Management User Guide” — SmartVID ve adaptif voltaj ölçekleme

Hands-on Eğitimler

- Xilinx, “Power Optimization Tutorial (UG997)” — Adım adım Vivado ile güç optimizasyonu

- AMD/Xilinx GitHub: “Vitis HLS Low Power Examples” — HLS seviyesinde güç odaklı tasarım örnekleri

İlgili Standartlar

- JEDEC JESD79-4: DDR4 SDRAM — DBI ve güç yönetimi özellikleri

- JEDEC JESD209-4: LPDDR4 — Mobil bellek arayüzlerinde düşük güç teknikleri

- IEEE 1801 (UPF): Unified Power Format — Güç intent’lerinin tanımlanması için endüstri standardı

Kaynakça

[1] I. Kuon and J. Rose, “Measuring the gap between FPGAs and ASICs,”

IEEE Trans. on Computer-Aided Design, vol. 26, no. 2, pp. 203-215, Feb. 2007.

[2] J. M. Rabaey, A. Chandrakasan, and B. Nikolić, “Digital Integrated Circuits:

A Design Perspective,” 2nd ed., Prentice Hall, 2003.

[3] Xilinx, “UltraFast Design Methodology Guide for FPGAs and SoCs (UG949),”

Xilinx Documentation, 2023.

[4] Xilinx, “Vivado Design Suite User Guide: Power Analysis and Optimization (UG907),”

Xilinx Documentation, 2023.

[5] Intel, “Power Analysis and Optimization User Guide,” Intel Quartus Prime

Pro Edition User Guide, 2023.

[6] S. Palnitkar, “Verilog HDL: A Guide to Digital Design and Synthesis,”

2nd ed., Prentice Hall, 2003.

[7] K. K. Parhi, “VLSI Digital Signal Processing Systems: Design and Implementation,”

Wiley, 1999.

[8] JEDEC, “JESD79-4C: DDR4 SDRAM Standard,” JEDEC Solid State Technology

Association, 2020.