Neden Sadece “Doğru” Çalışmak Yeterli Değil?

Sayısal tasarım dünyasına adım atan her mühendisin ilk öğrendiği şeylerden biri, bir devrenin sadece mantıksal olarak doğru çalışmasının yeterli olmadığıdır. Bir devrenin fonksiyonel olarak kusursuz olması, silikonda da beklendiği gibi çalışacağı anlamına gelmez. Eğer sinyaller olması gereken yere, olması gereken zamanda ulaşmazsa, en doğru mantık bile tamamen başarısız olur. Zamanlama, sayısal tasarımda pazarlığa kapalı, mutlak bir gerekliliktir.

Endüstri kaynaklarına göre, silikondaki tasarım hatalarının %80’inden fazlası zamanlama ihlallerinden kaynaklanmaktadır. Bu istatistik, konunun ciddiyetini tek başına ortaya koymaktadır. Bu nedenle, başarılı bir sayısal tasarım mühendisi olma yolundaki herkes için Statik Zamanlama Analizi (STA) ve temelindeki zamanlama kurallarını anlamak, kariyerlerinin en kritik adımıdır. Bu yazı dizisinde, bu temel kurallardan başlayarak ileri düzeydeki pratik çözümlere kadar STA’nın tüm yönlerini derinlemesine inceleyeceğiz.

Dijital Devrelerin Kalbi: Flip-Flop’lar ve Saat Sinyali

Senkron dijital tasarımların temel yapı taşı, kenar tetiklemeli D-Tipi Flip-Flop’lardır (Edge-Triggered D-Flip-Flop). Bu devre elemanları, sistemin “hafızası” olarak görev yapar ve veriyi belirli zaman anlarında yakalayıp saklayarak sıralı mantık devrelerinin temelini oluşturur.

Bu senkronize operasyonun orkestra şefi ise saat sinyalidir (clock signal). Tıpkı bir şefin orkestrayı yönetmesi gibi, saat sinyali de sistemin tüm parçalarına ortak bir zamanlama referansı sağlayarak her sürecin tam doğru anda ve uyum içinde tetiklenmesini garanti eder.

Flip-flop’lar, bu saat sinyalinin aktif kenarında (genellikle yükselen kenarında) girişlerindeki veriyi (D) örnekler ve çıkışlarına (Q) aktarırlar. Ancak bu örnekleme işleminin güvenilir olabilmesi için flip-flop’un uymak zorunda olduğu iki temel hız sınırı kuralı vardır: Setup ve Hold.

Hız Sınırları: Setup ve Hold Zamanı Nedir?

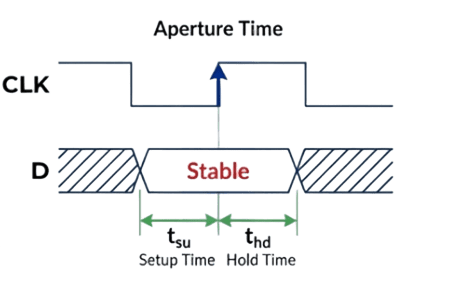

Bir flip-flop’un veriyi güvenilir bir şekilde yakalayabilmesi için, verinin aktif saat kenarı etrafında belirli bir süre boyunca kararlı kalması gerekir. Bu kararlılık penceresini tanımlayan iki kritik parametre Setup Zamanı (Tsu) ve Hold Zamanı (Th)’dır.

Setup Time (Kurulum Süresi) Verinin, aktif saat kenarından önce kararlı ve geçerli olması gereken minimum süredir.

Hold Time (Tutma Süresi) Verinin, aktif saat kenarından sonra kararlı kalması gereken minimum süredir.

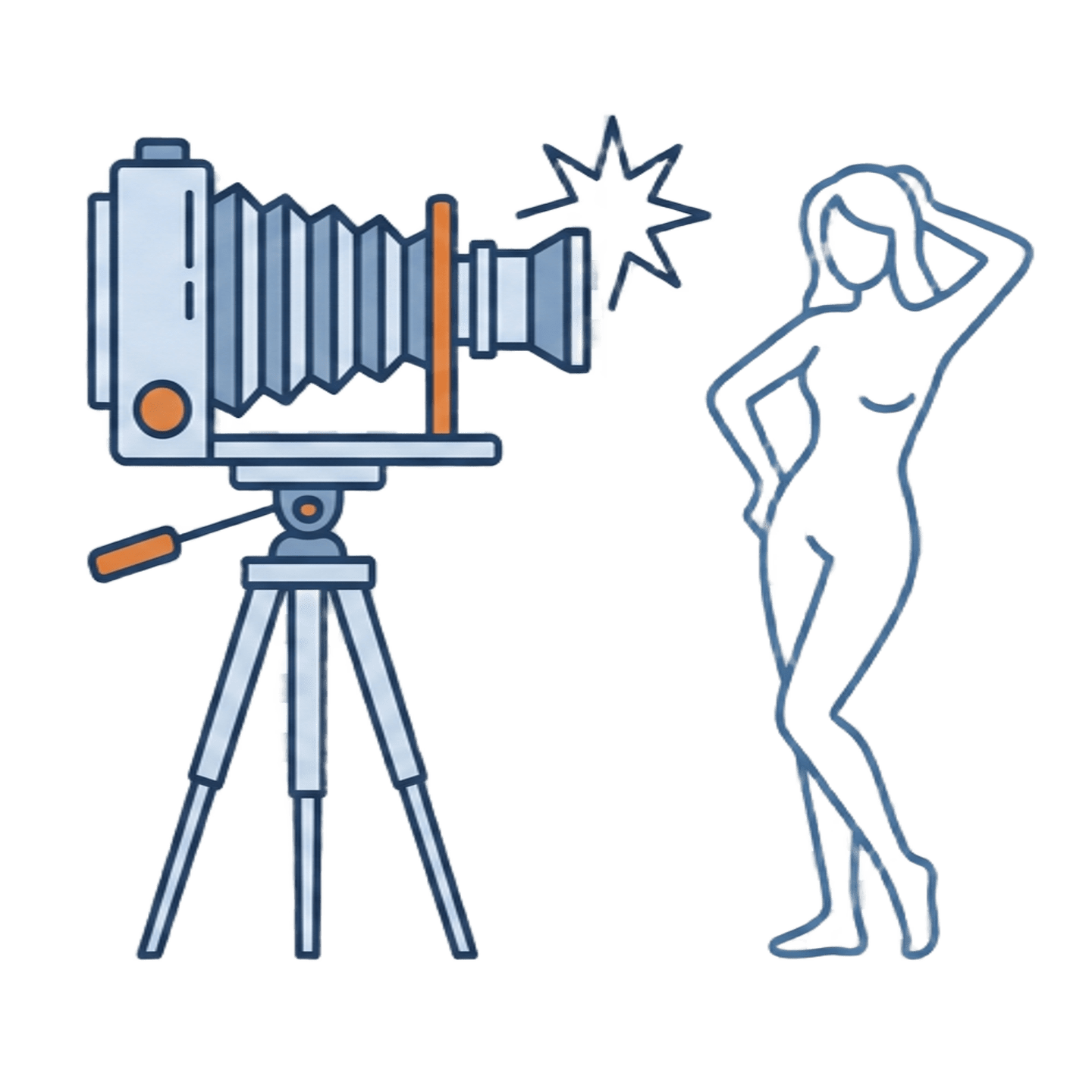

Bu kavramları daha iyi anlamak için bir fotoğrafçılık analojisi kullanalım:

Setup Time (Kurulum): Fotoğrafçı deklanşöre basmadan hemen önce modelin pozunu ayarlayıp hareketsiz kalması için gereken süredir. Model, flaş patlamadan (saat kenarı gelmeden) önce pozunu tamamlamış ve sabitlenmiş olmalıdır. Eğer veri çok geç gelirse (model pozunu zamanında ayarlayamazsa), fotoğraf anı kaçar.

Hold Time (Tutma): Flaş patladıktan hemen sonra, kameranın görüntüyü net bir şekilde yakalayabilmesi için modelin pozunu bir an daha bozmadan beklemesi gereken süredir. Eğer model flaş patlar patlamaz hemen hareket ederse (veri çok erken değişirse), fotoğraf bulanık çıkar (veri bozulur).

Flip-flop da verinin bu “mükemmel fotoğrafını” çekmek için hem öncesinde hazır olunmasını (Setup) hem de sonrasında pozun korunmasını (Hold) talep eder.

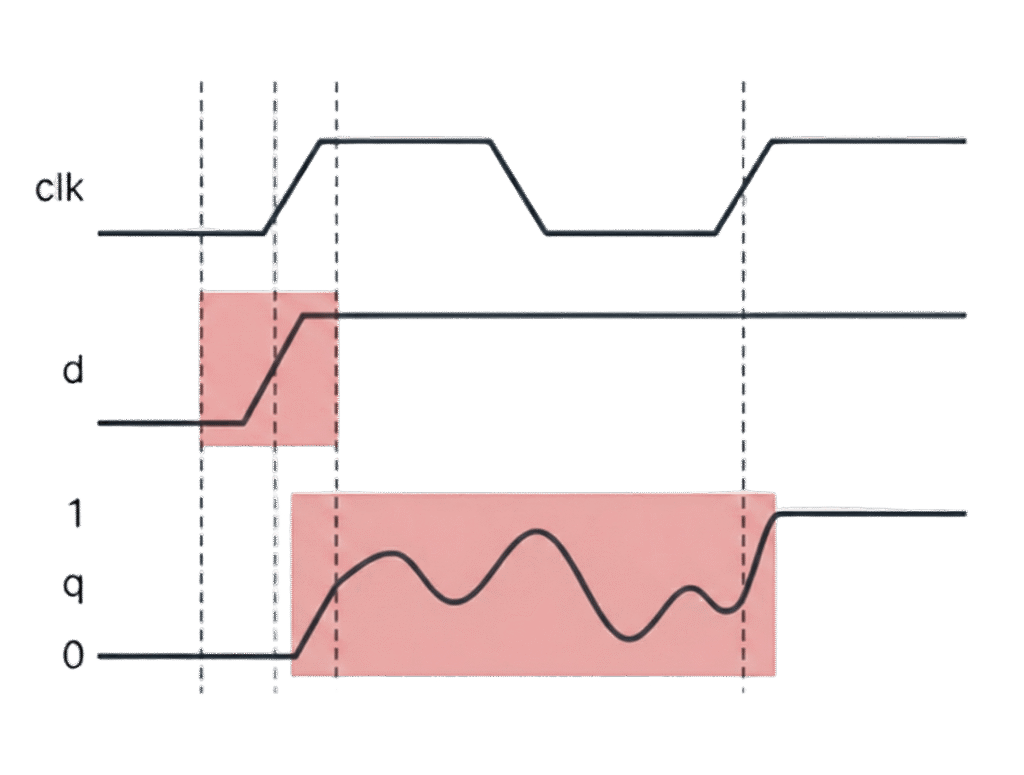

Kurallar Çiğnenince Ne Olur? Zamanlama İhlalleri ve Metastabilite

Eğer veri, flip-flop’un talep ettiği bu kritik Setup/Hold zaman penceresi içinde değişirse, bir zamanlama ihlali (timing violation) meydana gelir. Bu durum, flip-flop’un kararsız bir duruma girmesine neden olur.

Zamanlama ihlalinin en tehlikeli sonucu Metastabilite (Meta-İstikrarsızlık) durumudur. Metastabilite, flip-flop çıkışının ne net bir ‘0’ ne de net bir ‘1’ olabildiği, tahmin edilemez, yarı-kararlı bir durumdur. Bu belirsiz durumda çıkış voltajı, bir süre boyunca mantık seviyeleri arasında salınır. Bu kararsızlık, devrenin geri kalanına yayılırsa, tüm sistemin öngörülemez bir şekilde çalışmasına ve en sonunda çökmesine neden olabilir.

Bölüm Özeti

Bu bölümde, dijital tasarımlarda zamanlamanın neden mantıksal doğruluk kadar önemli olduğunu vurguladık. Senkron sistemlerin temelini oluşturan flip-flop’ları ve saat sinyalini tanıdık. En önemlisi, bir flip-flop’un veriyi doğru yakalayabilmesi için uyması gereken iki temel kural olan Setup ve Hold zamanlarını tanımladık. Bu kuralların ihlal edilmesi durumunda ortaya çıkan ve sistemler için büyük bir tehdit olan metastabilite kavramına giriş yaptık.